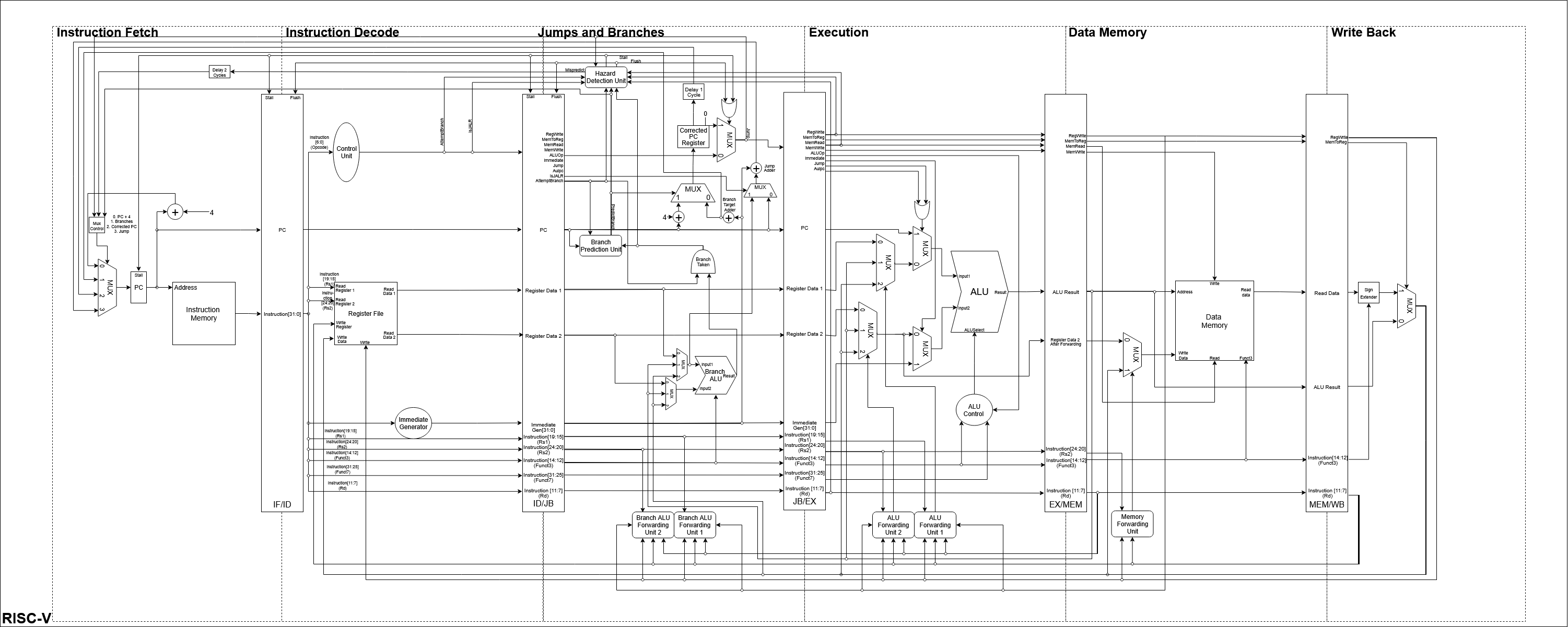

6 Stage Pipeline RISC-V Cpu

SystemVerilog-based implementation of a RISC-V CPU core with a 6 stage pipeline and various pipeline optimizations

Jun 2025 - Oct 2025 • 4 months

Tech Stack

SystemVerilogRTL DesignComputer ArchitectureStatic Timing Analysis

Description

This project implements a RISC-V CPU with to the RV32I instruction set architecture, using SystemVerilog. It consists of a 6 stage pipeline design with Fetch, Decode, Jumps/Branch Handling, Execution, Memory, and Write-Back stages. It contains data forwarding, hazard detection, and branch prediction.

Features

- Full support for the unpriveledged RV32I instruction set

- Implementation of datapath with many submodules for easier verification

- Various pipeline optimizations like data forwarding, hazard detection, and branch prediction to improve IPC

- Various testbenches for submodules in addition to master testbench for top level design