Systolic Array-based Matrix Multiplier for Neural Networks

Systolic Array-based Matrix Multiplier for Neural Networks (very in-progress)

Computer Engineer | Previously at Microsoft and Motorola Solutions

🇺🇸 US

University of Florida ECE Graduate seeking a career as an RTL Design Engineer. Contact me at [email protected].

I’m an aspiring RTL design engineer with a Master’s in Electrical and Computer Engineering from the University of Florida. I specialized in RTL design with my coursework and projects emphasizing development for FPGAs. My biggests interests in computer engineering are computer architecture and accelerator design. Although my previous internships with Microsoft and Motorola Solutions were in EMC Compliance and RF testing, I realized my passions truly lie in digital design. When I’m not spending time learning and developing hardware you can find me going to the gym, exploring live music in Miami, or learning guitar.

I've worked on a variety of RTL Design projects. Here is a sample of my projects.

Systolic Array-based Matrix Multiplier for Neural Networks (very in-progress)

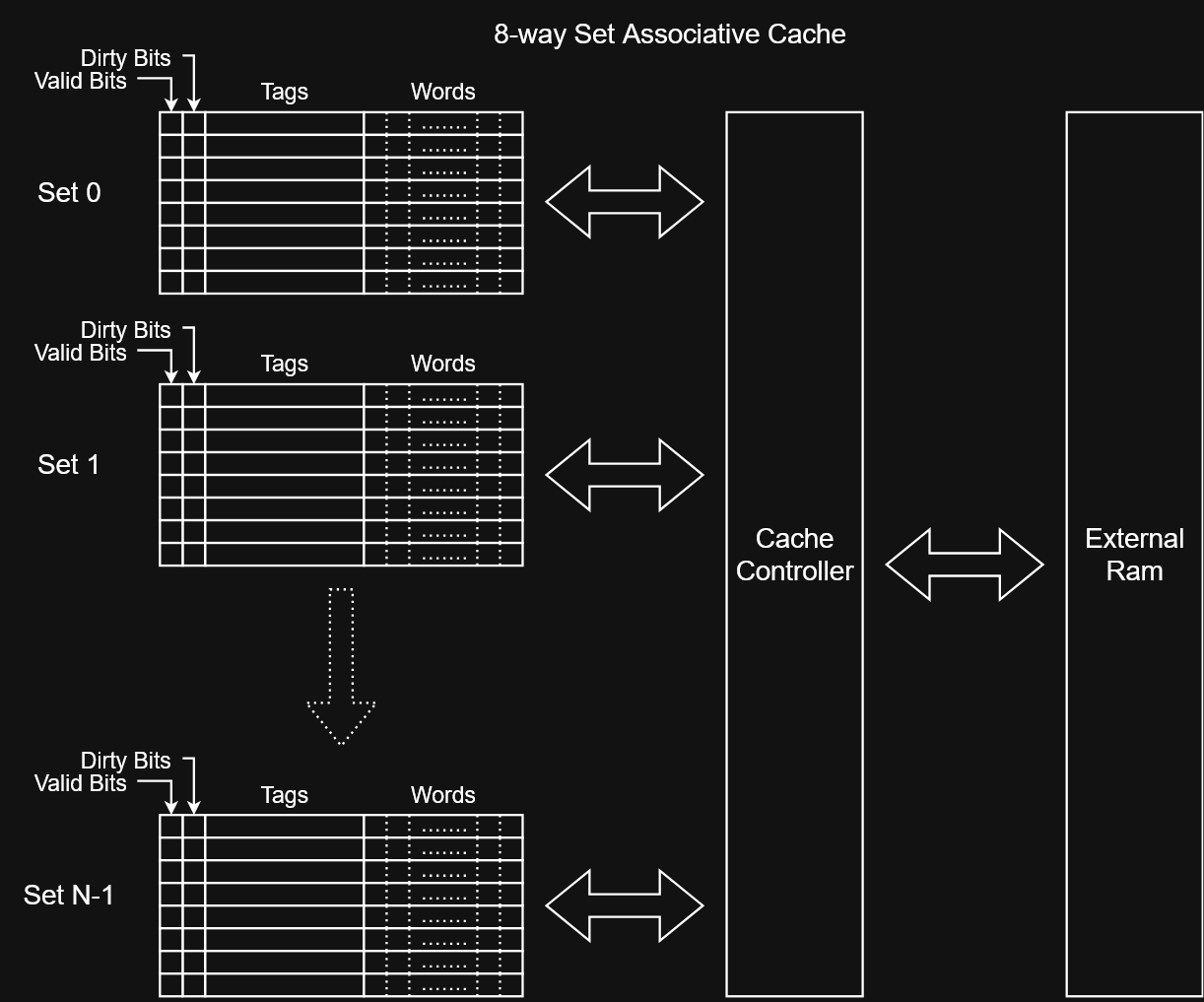

8-Way Set-Associative Cache Design in addition to a Fully-Associative and a Direct-Mapped Cache

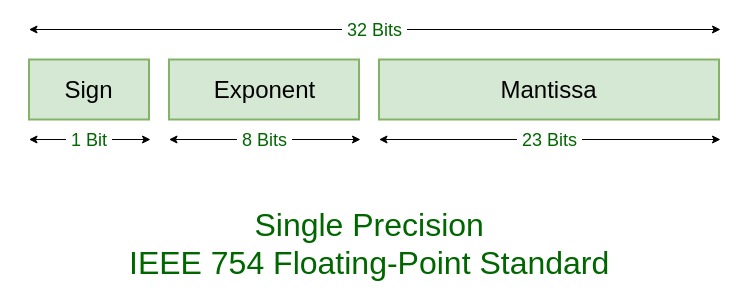

SystemVerilog-based design and FPGA implementation of a full-featured pipelined floating-point ALU

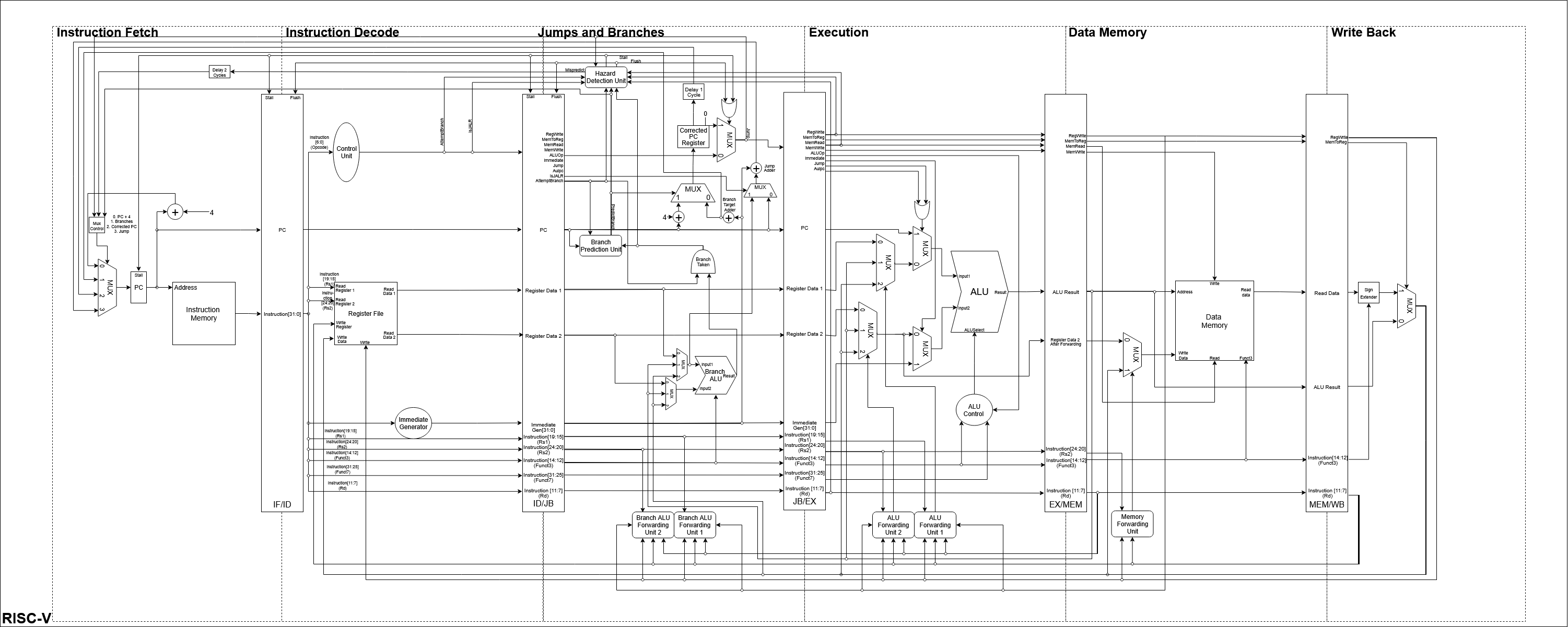

SystemVerilog-based implementation of a RISC-V CPU core with a 6 stage pipeline and various pipeline optimizations

Master of Science in Electrical and Computer Engineering

Focused on FPGA Design, Computer Architecture, Hardware Security, and VLSI Design. Graduated with a 3.89 gpa.

Bachelor of Electrical Engineering

Focused on digital design and embedded software engineering. Graduated with honors with a 3.7 GPA.